A métrica inflada que pode custar bilhões: o reflexo de desempenho em transistores 2D

Durante quase 20 anos, os semicondutores 2D têm funcionado como uma promessa conveniente: materiais como o dissulfeto de molibdênio (MoS₂) poderiam permitir canais ultradelgados, comutação eficiente e uma rota para reduzir ainda mais transistores quando o silício atingir limites práticos. A narrativa se apoiou em resultados de laboratório que, à primeira vista, pareciam demonstrar que o salto era iminente.

O problema é que grande parte dessa evidência comparativa pode estar construída sobre uma arquitetura de teste que não representa um futuro integrável a chips comerciais. Um estudo da Duke University, publicado em 17 de fevereiro de 2026 no ACS Nano, traz à tona uma verdade desconfortável: a configuração “back-gated”, muito usada por sua simplicidade experimental, pode inflar o desempenho medido em até seis vezes por um efeito chamado “contact gating”, que reduz a resistência de contato, mas impõe limites físicos que chocam com a realidade industrial, incluindo fugas de corrente e restrições de velocidade.

Como Analista de Diversidade, Equidade e Capital Social, minha leitura não é moral. É estratégica. Quando um campo inteiro se acostuma a medir "progresso" com instrumentos que premiam uma ilusão, o risco não se distribui: se concentra. O impacto é para o portfólio de P&D, para o roadmap tecnológico e para a reputação da liderança que apostou em métricas fáceis de celebrar.

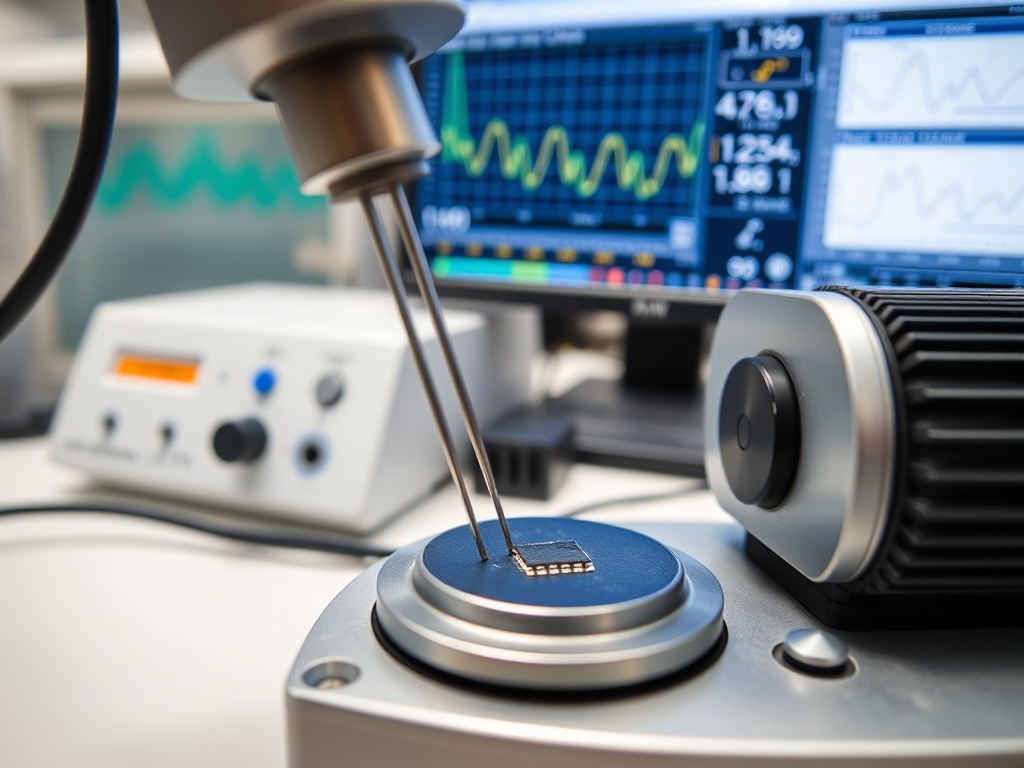

O achado de Duke: quando o desenho do experimento muda a física que se reporta

O time liderado por Aaron Franklin, com trabalho experimental da estudante de doutorado Victoria Ravel, comparou de forma controlada como se comportam transistores 2D quando se separa a porta que modula o canal da que afeta as regiões de contato. A arquitetura “back-gated” coloca o canal sobre um substrato de silício que atua como porta; essa porta não apenas modula o canal, mas também altera os contatos metálicos que injetam corrente. Esse “efeito duplo” é o cerne do contact gating.

Em termos de negócio, a diferença é brutal: o experimento não está medindo apenas o material. Está medindo um atalho arquitetônico. A pesquisa fabricou um desenho simétrico de dupla porta que permite ativar de modo independente uma porta superior ou traseira sobre o mesmo canal de MoS₂, isolando o efeito dos contatos. Em dispositivos maiores, o desempenho duplicou sob certas condições, o que já indica que a arquitetura importa mesmo antes de escalar.

Mas a mensagem que muda decisões aparece ao escalar para dimensões relevantes para chips futuros: com 50 nm de comprimento de canal e 30 nm de comprimento de contatos, o contact gating aumentou a corrente em estado “on” em cerca de 70% e elevou o desempenho reportado em até seis vezes. Franklin foi direto: “A maioria dos relatórios de transistores 2D de alto desempenho utiliza um design de dispositivo que não é compatível com tecnologias comerciais... pode inflar significativamente o desempenho”.

Isso não é um detalhe acadêmico. É um lembrete de que a indústria pode estar comparando maçãs com artefatos de laboratório. E quando se decide orçamento, aquisições, alianças e talentos com base em benchmarks distorcidos, castelos são construídos sobre areia.

A economia do hype técnico: quando um benchmark enviesado reordena capital e prioridades

O hype não nasce apenas do marketing. Em deep tech, o hype se produz por incentivos estruturais: publicar, demonstrar “estado da arte”, obter financiamento e sustentar uma narrativa de continuidade. Se o instrumento mais rápido para obter resultados “bons” é uma arquitetura de teste simples - e essa simplicidade se torna padrão - a disciplina inteira começa a se otimizar para o teste, e não para o produto.

Duke coloca números nessa distorção: até 6x de inflação não é uma margem de erro; é um multiplicador que altera decisões de portfólio. Sem dados financeiros específicos nas fontes, a implicação continua clara: o setor investe bilhões em P&D de semicondutores e em rotas de escalonamento onde um ponto percentual de desempenho ou energia move ciclos inteiros de investimento. Se uma parte da comunidade tem celebrado melhorias dependentes de um design não integrável por problemas de fugas e velocidade, o risco corporativo assume três formas.

Primeiro, risco de alocação de capital: financiam-se materiais ou abordagens que parecem superiores no “back gate”, mas perdem a vantagem ao passar para arquiteturas compatíveis. Segundo, risco de cronograma: roadmaps que assumem maturidade técnica próxima podem ser adiados quando os benchmarks são corrigidos. Terceiro, risco reputacional e de governança: quando um comitê de tecnologia não consegue explicar por que um salto de desempenho desaparece ao mudar o setup, a confiança do diretório na função de P&D se erosiona.

Franklin também aponta para uma tensão típica: “Amplificar desempenho parece uma coisa boa... mas... possui limitações físicas que impedem que seja usada em uma tecnologia de dispositivo real”. Traduzindo para a linguagem C-Level: o laboratório pode estar maximizando um KPI que o mercado não paga. Essa é a maneira mais cara de progresso.

O ponto cego organizacional: homogeneidade técnica e redes fechadas que normalizam o erro

Aqui aparece meu foco: a distorção não é apenas de arquitetura elétrica; é de arquitetura social. Durante duas décadas, uma prática de benchmarking se normalizou. Isso raramente ocorre porque "ninguém sabia". Ocorre porque as redes que validam conhecimento - revisores, laboratórios de referência, líderes de opinião - tendem a ser fechadas e autorreferenciais. Quando a rede é excessivamente vertical, o poder de definir o que é “bom desempenho” se concentra.

O estudo descreve um fenômeno que “afeta a maioria dos testes de laboratório” e que exige reevaluar centenas de estudos anteriores. Esse tipo de correção de campo requer algo mais do que um artigo: requer capacidade de dissentimento técnico dentro das comunidades que fixam padrões. Em organizações corporativas, isso se traduz em equipes que não sejam clones de formação, incentivos e contatos.

Uma equipe diretiva homogênea tende a falhar em uma mecânica específica: confunde consenso com verdade. Se a mesa técnica compartilha a mesma origem acadêmica, os mesmos congressos, o mesmo circuito de validação e os mesmos “gurus”, o sistema se torna frágil diante de um viés de metodologia. Não é necessário má fé. Basta um circuito de reputação que recompensa resultados “comparáveis” e pune desvios do setup dominante.

A lição operacional é desconfortável: a diversidade útil em deep tech não é cosmética. É diversidade de disciplina (fabricação, design, integração, confiabilidade, manufatura), diversidade de incentivos (pesquisa vs. produto), e diversidade de redes (pessoas que não dependem do mesmo capital social para progredir). Em termos de execução, o contact gating funcionou como um “atalho” durante anos porque era fácil de usar e produzia números atraentes. Redes fechadas tornam esses atalhos em dogma.

Quando Franklin afirma “precisamos ser honestos sobre como a arquitetura do dispositivo molda o que medimos”, ele está descrevendo, indiretamente, uma falha de governança do conhecimento: se o padrão de medição premia um reflexo, o ecossistema inteiro corre na direção errada.

O que um C-Level deveria exigir desde amanhã: benchmarks integráveis e uma rede técnica que saiba dizer não

O valor do estudo não é desmotivar os 2D. É forçar um mudança de disciplina: separar descoberta de material de arquitetura de teste e de compatibilidade com integração comercial. Duke propõe uma base: desenhos como o dual-gate para avaliar de forma mais justa e reprodutível. Além disso, a equipe planeja escalar comprimentos de contato para 15 nm e testar metais alternativos para reduzir resistência de contato dentro das restrições compatíveis.

Para o C-Level, isso se transforma em uma lista de verificação de controle, não em uma discussão acadêmica:

- Reavaliação dos KPIs de P&D: exigir que qualquer “registro” de desempenho em 2D venha acompanhado pelo setup e por uma explicação explícita se a arquitetura é integrável ou apenas demonstrativa. O número sem contexto já não é evidência.

- Governança de validação: impor revisões cruzadas com perfis que não estejam capturados pelo mesmo circuito de publicações. Isso inclui engenharia de manufatura, confiabilidade e pessoas que tenham vivido transições tecnológicas onde os benchmarks foram rompidos ao industrializar.

- Arquitetura de capital social: construir relações horizontais com laboratórios e equipes que possam contradizer a narrativa dominante sem pagar o custo reputacional de “sair do padrão”. Em inovação difícil, a rede mais valiosa não é a que aplaude primeiro; é a que detecta a falha antes.

A indústria de semicondutores não pode permitir mais duas décadas de otimização para a vitrine do laboratório. A mensagem de Duke é um chamado à maturidade: medir como se fabrica, e fabricar como se vende.

O mandato para a liderança corporativa é direto: na próxima reunião de diretoria, o C-Level deve olhar sua mesa pequena e reconhecer que se todos são muito parecidos, compartilham os mesmos pontos cegos e acabam posicionados como vítimas iminentes da disrupção.