La métrica inflada que puede costar miles de millones: el espejismo de rendimiento en transistores 2D

Durante casi 20 años, los semiconductores 2D han funcionado como una promesa conveniente: materiales como el disulfuro de molibdeno (MoS₂) podrían permitir canales ultradelgados, conmutación eficiente y una ruta para seguir reduciendo transistores cuando el silicio llegue a límites prácticos. La narrativa se apalancó en resultados de laboratorio que, a simple vista, parecían demostrar que el salto era inminente.

El problema es que gran parte de esa evidencia comparativa puede estar construida sobre una arquitectura de prueba que no representa un futuro integrable a chips comerciales. Un estudio de Duke University publicado el 17 de febrero de 2026 en ACS Nano aterriza una verdad incómoda: la configuración “back-gated”, muy usada por su simplicidad experimental, puede inflar el rendimiento medido hasta seis veces por un efecto llamado “contact gating”, que reduce la resistencia de contacto pero impone límites físicos que chocan con la realidad industrial, incluyendo fugas de corriente y restricciones de velocidad.[1]

Como Analista de Diversidad, Equidad y Capital Social, mi lectura no es moral. Es estratégica. Cuando un campo entero se acostumbra a medir “progreso” con instrumentos que premian una ilusión, el riesgo no se distribuye: se concentra. Lo paga el portafolio de I+D, lo paga el roadmap tecnológico y lo paga la reputación del liderazgo que apostó por métricas fáciles de celebrar.

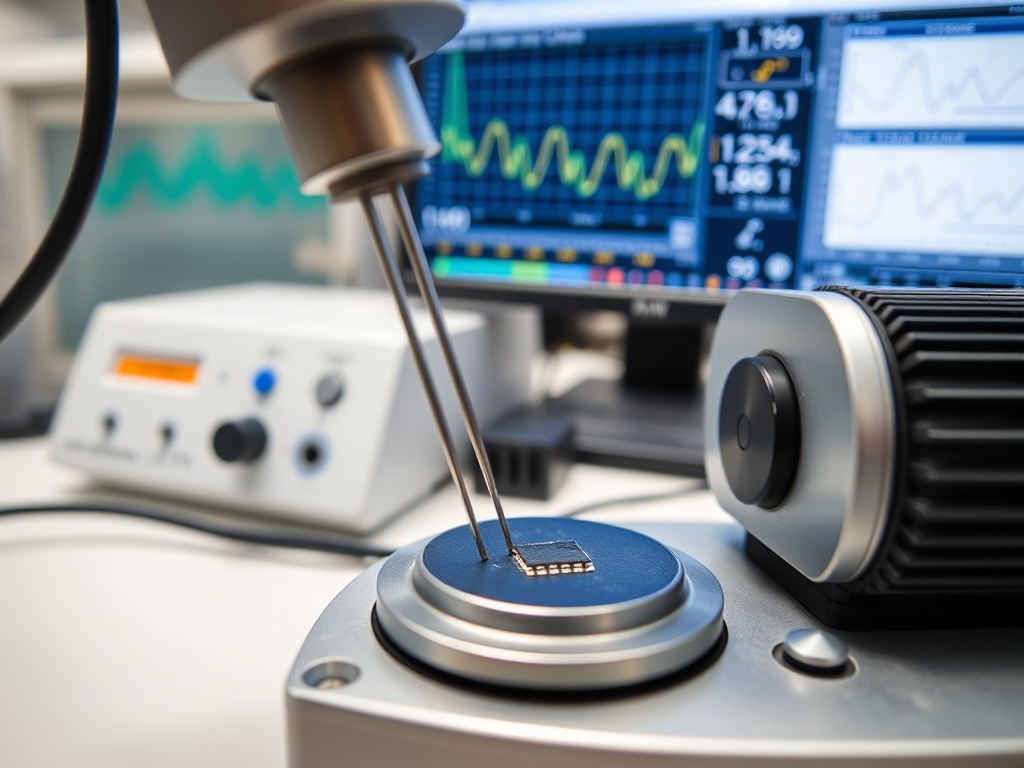

El hallazgo de Duke: cuando el diseño del experimento cambia la física que se reporta

El equipo liderado por Aaron Franklin, con trabajo experimental clave de la Ph.D. student Victoria Ravel, comparó de forma controlada cómo se comportan transistores 2D cuando se separa la compuerta que modula el canal de la que afecta las regiones de contacto.[1] La arquitectura “back-gated” coloca el canal sobre un sustrato de silicio que actúa como compuerta; esa compuerta no solo modula el canal, también altera los contactos metálicos que inyectan corriente. Ese “doble efecto” es el corazón del contact gating.

En términos de negocio, la diferencia es brutal: el experimento no está midiendo únicamente el material. Está midiendo un atajo arquitectónico. La investigación fabricó un diseño simétrico de doble compuerta que permite activar de manera independiente una compuerta superior o trasera sobre el mismo canal de MoS₂, aislando el efecto de los contactos.[1] En dispositivos más grandes, el desempeño se duplicó bajo ciertas condiciones, lo que ya señala que la arquitectura importa incluso antes de escalar.[1]

Pero el mensaje que cambia decisiones aparece al escalar a dimensiones relevantes para chips futuros: con 50 nm de longitud de canal y 30 nm de longitud de contactos, el contact gating incrementó la corriente en estado “on” cerca de 70% y elevó el desempeño reportado hasta seis veces.[1] Franklin lo dijo sin rodeos: “Most reports of high-performance 2D transistors use a device design that isn't compatible with commercial technologies… can significantly inflate performance”.[1]

Esto no es un detalle académico. Es un recordatorio de que la industria puede estar comparando manzanas con artefactos de laboratorio. Y cuando se decide presupuesto, adquisiciones, alianzas y talento sobre benchmarks distorsionados, se construyen castillos sobre arena.

La economía del hype técnico: cuando un benchmark sesgado reordena capital y prioridades

El hype no nace solo del marketing. En deep tech, el hype se produce por incentivos estructurales: publicar, demostrar “state of the art”, obtener financiamiento y sostener una narrativa de continuidad. Si el instrumento más rápido para obtener resultados “buenos” es una arquitectura de prueba simple —y esa simplicidad se vuelve estándar—, la disciplina completa empieza a optimizar para el test, no para el producto.

Duke pone números a esa distorsión: hasta 6x de inflación no es un margen de error; es un multiplicador que altera decisiones de portafolio. Sin datos financieros específicos en las fuentes, la implicación sigue siendo clara: el sector invierte miles de millones en I+D de semiconductores y en rutas de escalamiento donde un punto porcentual de rendimiento o energía mueve ciclos de inversión completos. Si una parte de la comunidad ha estado celebrando mejoras que dependen de un diseño no integrable por problemas de fugas y velocidad, el riesgo corporativo toma tres formas.

Primero, riesgo de asignación de capital: se financian materiales o enfoques que lucen superiores en el “back gate”, pero pierden la ventaja al pasar a arquitecturas compatibles. Segundo, riesgo de cronograma: roadmaps que asumen madurez técnica cercana pueden atrasarse cuando se corrigen los benchmarks. Tercero, riesgo reputacional y de gobernanza: cuando un comité de tecnología no puede explicar por qué un salto de rendimiento desaparece al cambiar el setup, la confianza del directorio en la función de I+D se erosiona.

Franklin también apunta a una tensión típica: “Amplifying performance sounds like a good thing… but… has physical limitations that prevent it from being used in an actual device technology”.[1] Traducido al lenguaje C-Level: el laboratorio puede estar maximizando un KPI que el mercado no paga. Esa es la forma más cara de progreso.

El punto ciego organizacional: homogeneidad técnica y redes cerradas que normalizan el error

Aquí aparece mi lente: la distorsión no es solo de arquitectura eléctrica; es de arquitectura social. Durante dos décadas, una práctica de benchmarking se normalizó. Eso rara vez ocurre porque “nadie sabía”. Ocurre porque las redes que validan conocimiento —revisores, laboratorios de referencia, líderes de opinión— tienden a ser cerradas y autorreferenciales. Cuando la red es demasiado vertical, el poder de definir qué es “buen rendimiento” se concentra.

El estudio describe un fenómeno que “afecta a la mayoría de las pruebas de laboratorio” y que exige reevaluar cientos de estudios previos.[1] Ese tipo de corrección de campo requiere algo más que un paper: requiere capacidad de disenso técnico dentro de las comunidades que fijan estándares. En organizaciones corporativas, eso se traduce en equipos que no sean clones de formación, incentivos y contactos.

Un equipo directivo homogéneo suele fallar en una mecánica específica: confunde consenso con verdad. Si la mesa técnica comparte el mismo origen académico, los mismos congresos, el mismo circuito de validación y los mismos “gurús”, el sistema se vuelve frágil ante un sesgo de metodología. No hace falta mala fe. Alcanza con un circuito de reputación que recompensa resultados “comparables” y castiga desviarse del setup dominante.

La lección operativa es incómoda: la diversidad útil en deep tech no es cosmética. Es diversidad de disciplina (fabricación, diseño, integración, confiabilidad, manufactura), diversidad de incentivos (investigación vs. producto), y diversidad de redes (gente que no depende del mismo capital social para progresar). En términos de ejecución, el contact gating funcionó como “atajo” durante años porque era fácil de usar y producía números atractivos. Las redes cerradas convierten esos atajos en dogma.

Cuando Franklin afirma “we need to be honest about how device architecture shapes what we measure”,[1] está describiendo, indirectamente, una falla de gobernanza del conocimiento: si el estándar de medición premia un espejismo, el ecosistema entero corre en la dirección equivocada.

Lo que un C-Level debería exigir desde mañana: benchmarks integrables y una red técnica que sepa decir no

El valor del estudio no es desalentar los 2D. Es forzar un cambio de disciplina: separar descubrimiento de material de arquitectura de prueba y de compatibilidad con integración comercial. Duke propone una base: diseños como el dual-gate para evaluar de forma más justa y reproducible.[1] Además, el equipo planea escalar longitudes de contacto a 15 nm y probar metales alternativos para reducir resistencia de contacto dentro de restricciones compatibles.[1]

Para el C-Level, esto se convierte en un checklist de control, no en una discusión académica:

- Replanteo de KPIs de I+D: exigir que cualquier “récord” de desempeño en 2D venga acompañado por el setup y por una explicación explícita de si la arquitectura es integrable o solo demostrativa. El número sin contexto ya no es evidencia.

- Gobernanza de validación: imponer revisiones cruzadas con perfiles que no estén capturados por el mismo circuito de publicaciones. Eso incluye ingeniería de manufactura, confiabilidad, y gente que haya vivido transiciones tecnológicas donde los benchmarks se rompieron al industrializar.

- Arquitectura de capital social: construir relaciones horizontales con laboratorios y equipos que puedan contradecir la narrativa dominante sin pagar el costo reputacional de “irse del estándar”. En innovación dura, la red más valiosa no es la que aplaude primero; es la que detecta la falla antes.

La industria de semiconductores no puede permitirse dos décadas más de optimización para la vitrina del laboratorio. El mensaje de Duke es una llamada a madurar: medir como se fabrica, y fabricar como se vende.

El mandato para el liderazgo corporativo es directo: en la próxima reunión de directorio, el C-Level debe mirar su mesa chica y reconocer que si todos son demasiado parecidos, comparten los mismos puntos ciegos y quedan posicionados como víctimas inminentes de la disrupción.